- ADD DSP BUILDER TO QUARTUS PROJECT INSTALL

- ADD DSP BUILDER TO QUARTUS PROJECT SOFTWARE

- ADD DSP BUILDER TO QUARTUS PROJECT CODE

The regression ensures the design template passes analysis/synthesis/fitting/assembly steps in the Quartus design flow. Quartus Prime software provides everything you need to design with Altera devices. Note: When a design is stored in the Design Store as a design template, it has been previously regression tested against the stated version of Quartus software. par file you downloaded, click next, followed by Finish, and your design template will be installed and displayed in the Project Navigator pane in Quartus.

ADD DSP BUILDER TO QUARTUS PROJECT INSTALL

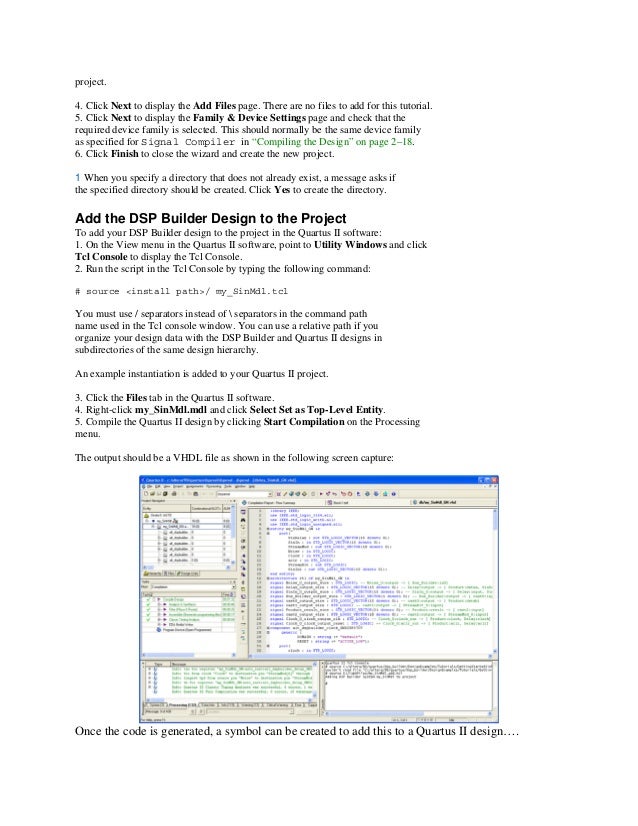

If you don't see your design template in the list, click on the link that states install the Design Templates circled below:īrowse to the. You will see a list of Design Templates projects that you have loaded prior as well as various "Baseline Pinout Designs" that contain the pinout and settings for a variety of development kits. DSP Builder is an add-on tool to the Mathworks MATLAB and Simulink toolset. After entering the project name and folder on the first panel, the second panel will ask you to specify an empty project or project template. In applications where no co-processors are available, Altera is developing. We need to add both the nonlinear subsystem and nonlinear synthesizable subsystem from our DSP builder design to our Quartus project. The second means to bring up the project template is through the New Project Wizard (File -> New Project Wizard).

Purchase MATLAB license here Required order of installation is 1. par file and Quartus will launch that project. Additional DSP Builder and MATLAB licenses are required. In releases 16.0 or newer, you can simply double click on the. The combination of this information is what constitutes a. From within Quartus I simply change the VHDL version in project settings and all is well.

ADD DSP BUILDER TO QUARTUS PROJECT CODE

In the sensitivity list for some of my processes in my hand written code I use the 'all' keyword, which apparently is only valid for VHDL 2008. qar file) and metadata describing the project. I installed Quartus and DSP Builder v10 today and am already having trouble. par file which contains a compressed version of your design files (similar to a. Qsys system integration tool, state machine editor, memory editor, Altera SD for OpenCL, and DSP Builder are also introduced in high level. The file you downloaded is of the form of a. The course starts with an overview of the Quartus Prime design software features, Quartus Prime projects types and management, design methodology, and using IP cores from the IP catalog. Note: After downloading the design example, you must prepare the design template.

0 kommentar(er)

0 kommentar(er)